三星 3 纳米芯片成功流片 有望明年实现量产

GAA 架構實現了柵極對通道之間的四面環繞,被廣泛認為是 FinFET 的繼任者。三星和台積電作為全球唯二能做到 5 納米制程以下的半導體晶圓代工廠,此番共同角逐 GAA 舞台,較勁意味濃厚。

據媒體報道,三星採用全環繞柵極架構(Gate-All-Around FET,GAA)的 3 納米制程技術已正式流片,性能上優於台積電的鰭式場效應架構(FinFET)。

流片即 tape-out,在芯片設計領域指試生產,當電路設計完成以後,像流水線一樣通過一系列工藝步驟製造芯片,以供測試之用。

報道稱,三星在 3nm 製程的流片進度是與新思科技(Synopsys)合作完成的。根據新思科技公告,其 Synopsys Fusion 設計平台加速為 GAA 架構的生產流程提供高度優化參考方法,使其在功率和性能上均實現最大化。

製程技術的物理設計套件(PDK)已在 2019 年 5 月發佈,並 2020 年通過製程技術認證。媒體稱,預計此流程使三星 3nm GAA 結構製程技術用於高性能運算(HPC)、5G、行動和高階人工智能(AI)應用芯片生產。

伴隨此次成功流片,三星 3 納米芯片大規模量產或已臨近。

GAA FET:FinFET的繼任者

專家稱,相比台積電或英特爾所採用的 3nm FinFET 架構,在技術性能上,GAA 架構的晶體管能夠提供比 FinFET 更好的靜電特性,可滿足某些柵極寬度的需求。

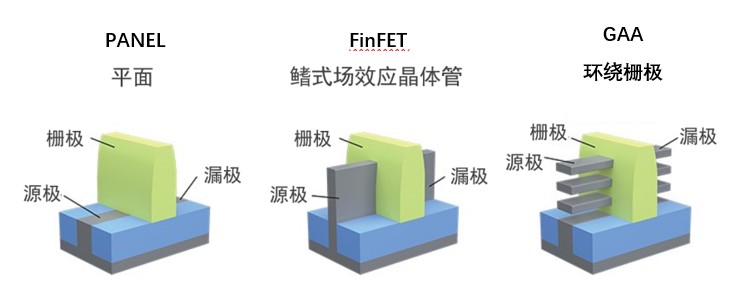

對於場效應晶體管(Field Effect Transistor,FET)來説,決定其效率的一個重要因素就是柵極對通道的控制能力。

自英特爾在 22 納米節點上首次採用 FinFET 架構以來,過去十年,FinFET 一直是半導體器件的主流架構。與最初的平面晶體管相比,與柵極三面接觸的 “鰭” 所形成的通道更容易控制。

圖片來源:Lam Research

但是,雖然 “鰭” 的三面均受柵極控制,仍然有一側未被接觸。5 納米節點之後,隨着柵極長度縮短,短溝道效應越發明顯,FinFET 結構已經很難滿足晶體管所需的電流驅動和靜電控制能力,更多電流通過器件底部無接觸的部分泄露,漏電現象急劇惡化。

隨着半導體技術繼續發展,晶體管尺寸要進一步縮小,就必須找到新的解決方案。

基於此,GAA 架構實現了柵極對通道之間的四面環繞,被廣泛認為是 FinFET 的繼任者。

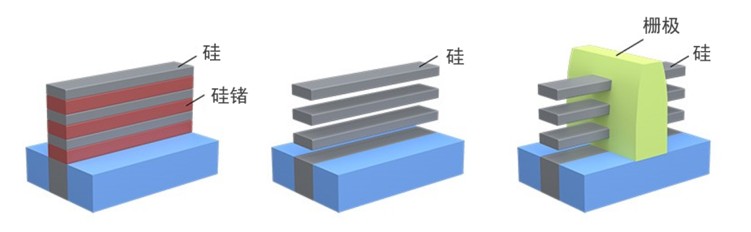

據 Nerissa Draeger 博士,GAA 架構以納米薄片代替鰭片,不同於 FinFET 必須並排多個鰭片才能提高電流,GAA 晶體管只需多垂直堆疊幾個納米薄片並讓柵極包裹通道就能夠獲得更強的載流能力。這使得同等尺寸結構下,GAA對通道控制能力強化,尺寸進一步微縮更具可能性。

圖片來源:Lam Research

隨着芯片技術進步,薄片的寬度和間隔也會不斷縮減,納米薄片看起來會更像 “納米線”,則溝道整個外輪廓都將被柵極完全包裹,代表柵極對溝道的控制性更好。

角逐GAA舞台

新型晶體管方案已經受到多家半導體廠商青睞。

在 2019 年的三星晶圓製造論壇上,三星就明確表示將會在 3 納米節點放棄鰭式結構,轉向全環繞柵極技術。去年台積電第 26 屆技術研討會上,台積電也正式宣佈將在 2 納米節點引入全環繞柵極技術。

而就在 6 月 2 日召開的 2021 年線上技術論壇上,台積電剛剛宣佈其3納米制程預計在2022年投入量產,並表示到那時,3 納米將成為全球最先進的技術。

目前,三星和台積電是全球唯二能做到5納米制程以下的半導體晶圓代工廠,此番共同角逐GAA舞台,較勁意味濃厚。

三星代工設計技術團隊副總裁 Sangyun Kim 表示,三星代工是推動下一階段產業創新的核心。三星將藉由不斷發展技術製程,滿足專業和廣泛市場增長的需求。

新思科技數字設計部總經理 ShankarKrishnamoorthy 也表示:

GAA 晶體管結構象徵着製程技術進步的關鍵轉折點,對保持下一波超大規模創新所需的策略至關重要。

新思科技與三星戰略合作支持提供一流技術和解決方案,確保發展趨勢延續,以及為半導體產業提供機會。

此外,英特爾雖仍然受困於 7 納米技術,其首席技術官麥克邁克·梅伯裏博士也在今年的國際 VLSI 會議上稱,希望英特爾能在 5 年之內實現 GAA 晶體管的量產。