週末熱議的 Chiplet ,會帶火哪些半導體細分?

Chiplet 工藝對半導體產業鏈影響最大的是封裝和測試環節,芯片設計是測試機需求的先驗指標。

Chiplet 工藝對半導體產業鏈影響最大的是封裝和測試環節,芯片設計是測試機需求的先驗指標。

近日 Chiplet 的概念大火,作為延續摩爾定律的一個重要技術到底説了些什麼?又會影響到半導體產業鏈的哪些環節?

首先,要了解到 Chiplet 是一種製造和封裝芯片的方法。其最重要的技術突破在於封裝,其次是測試。

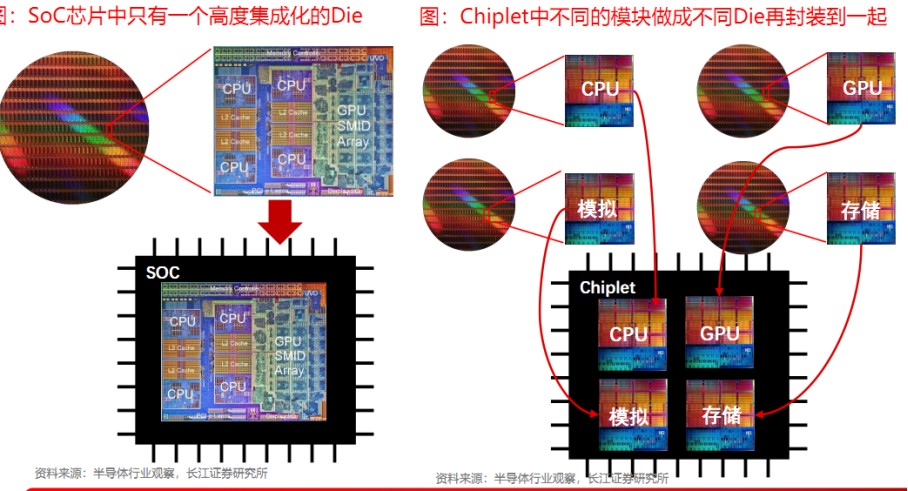

可作為對比的是:現在普遍採用 SOC 模式,從下圖中可以清晰可見。兩種工藝的不同指出在於,SOC 是把載有不同功能的模塊都封裝在同一晶圓中;而 Chiplet 是將模塊進行歸類劃分,先封裝成幾個不同的裸片,最後再封裝到一起。也就是説 Chiplet 比 SOC 多了一組封裝的流程。

兩種工藝的重點區別

首先,SOC 模塊要求封裝的必須是相同製程的模塊,比如 GUP、CUP、存儲都必須是 7nm 製程;

而 Chiplet 因為是進行分別封裝的,所以對第一次集成裸片的工藝要求沒有那麼苛刻,比如説封裝一個 7nm 的 CPU、14nm 的存儲芯片,130nm 的模擬芯片,接下來就是最後一步,將這些已封裝好的裸片再次封裝到一起。

所以,最後一個封裝環節就變得極為關鍵,因為要將不同工藝,或者不同材質的模塊(比如 Si、SiC、GaN)集成在一起。這裏會涉及到電路接口、信號傳輸、裸片位置放置的佈局設計,就存在非常複雜的情況,對封裝廠的技術有了更高的要求。

這也就是為什麼要成立 Chiplet 生態聯盟的重要原因之一。隨着關鍵傳輸協議標準的形成、各個功能區域模塊的鏈接方式統一,那麼 Chiplet 的應用才可能被大範圍推廣。

測試需求顯著增加

非常明顯的是,Chiplet 要比 SoC 進行更多次的封裝,也就需要進行更多次測試檢驗,以確保每個裸片都是可以正常運作的,不然一單存在單一模塊性能失效,後面的封裝也就是做無用功,所以多次檢測的目的是為了能夠提高出貨良品率。

從晶圓上的裸片來看,理論上 Chiplet 的良率是會明顯高於 SOC 的,因為要切割的模塊單位面積變小了,晶圓上如果存在污染點對於模塊影響的概率要降低一些。

而另一方面,Chiple 工藝在不同晶圓上切割下來的模塊數量會更多,但是隨着模塊性能進行分類集成,對於芯片廠商的生產能力要求也開始降低,可以通過採購不同模塊進行集成,很大程度優化了先進工藝的生產流程。

總的來看,Chiplet 工藝對於測試機的需求要高於 SOC 工藝。而測試機是具有非常高的技術壁壘,其關鍵點在於做數據處理的測試軟件平台以及用於數據傳輸的內部板卡,這將會是測試機廠商的核心競爭力所在。

芯片設計是測試機訂單先驗者

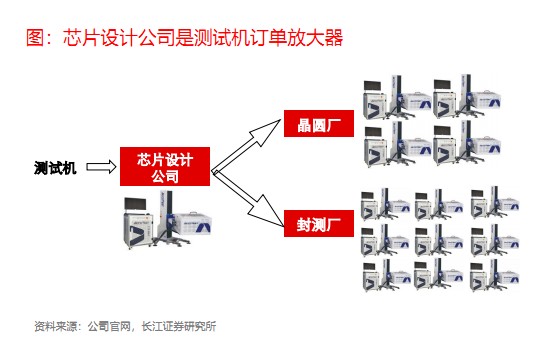

從產業鏈生態環節來看,測試機的直接下游首先是芯片設計公司,再者是晶圓廠和封測廠,而後兩者的採購量要遠遠高於前者。

芯片設計公司會先與自己的客户進行芯片需求溝通交流來設計方案,同時也會採購少量的測試機,通過了這個環節後,才會驅動才下游代工廠和封裝廠進行採購。

最終下游的真實裝機量是與設計公司以及客户數量構成完整的生態閉環。對於該生態來説,每一環都緊緊相扣,一旦通過客户認證則具備非常強的粘性。

風險提示及免責條款

市場有風險,投資需謹慎。本文不構成個人投資建議,也未考慮到個別用户特殊的投資目標、財務狀況或需要。用户應考慮本文中的任何意見、觀點或結論是否符合其特定狀況。據此投資,責任自負。